|

|

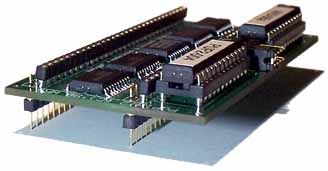

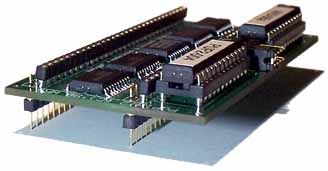

PuPla/2

Buspufferplatine und Interruptlogik

für die PAK68/3 und Panther/2

|

Impressum |

|

|

Bus-Pufferplatine und Interruptlogik

für die PAK68/3 und Panther/2

Entwickler: Holger Zimmermann, Roland Skuplik

Copyright © 1998-2000 WRS Software-Design

Alle Rechte vorbehalten. Das Copyright an der Hardware-Erweiterung PuPla/2,

einschließlich der GAL-Gleichungen, liegt bei den Entwicklern.

Vervielfältigung ist ausschließlich zu privaten Zwecken erlaubt!

Distributor/Bezugsquelle:

WRS Software-Design

W. Rohmann & R. Skuplik GbR

Humboldtstraße 12

45886 Gelsenkirchen

Email: info [ at ] wrsonline [ dot ] de

Dokumentation: R. Skuplik, H. Zimmermann

HTML-Version vom 07.03.2000

Einschränkung der Gewährleistung

Änderungen an der Hardware, den GAL-Gleichungen oder der

Dokumentation behalten wir uns ohne Einschänkung vor. Es

wird keine Haftung für die Richtigkeit des Handbuches oder

Schäden, die sich aus dem Gebrauch der Hardware ergeben,

übernommen. Jeder Ein-/Umbau an der eigenen Rechneranlage geschieht

grundsätzlich auf eigene Gefahr!

Für Hinweise zur Verbesserung des Handbuches sind wir jederzeit

dankbar.

|

|

Inhaltsverzeichnis |

|

|

1. |

Vorweg |

|

|

1.1 |

Hinweise |

|

|

1.2 |

Lieferumfang |

|

|

1.3 |

Voraussetzungen |

|

|

1.4 |

Funktionsumfang der PuPla/2 |

| |

|

|

2. |

Aufbau der PuPla/2 |

|

|

2.1 |

Voraussetzungen |

|

|

2.2 |

Der Aufbau |

| |

|

|

3. |

Einbau der PuPla/2 |

|

|

3.1 |

Vorbereitungen |

|

|

3.2 |

Der Einbau ohne PAK / DIL-CPU |

|

|

3.3 |

Der Einbau mit PAK / DIL-CPU |

|

|

3.4 |

Der Einbau ohne PAK / PLCC-CPU |

|

|

3.5 |

Der Einbau mit PAK / PLCC-CPU |

| |

|

|

4. |

Konfiguration |

|

|

4.1 |

Jumper |

|

|

4.2 |

PuPla/2-GALs |

| |

|

|

|

Anhang |

|

|

A |

Bestückungsplan |

|

|

B |

Stückliste |

| |

|

1. Vorweg |

|

|

1.1 |

Hinweise |

|

|

Lesen Sie bitte die Anleitung zum Auf- und Einbau

der PuPla/2 genau durch, bevor Sie beginnen. Die meisten Fehler lassen

sich auf unzureichende Kenntnis der Anleitung zurückführen!

Der Einbau des PuPla/2-Fertiggerätes sollte

auch für Leute mit wenig Hardware-Erfahrung durchführbar sein.

Wer sich trotzdem die nötigen Arbeitsschritte nicht zutraut,

möge bitte Kontakt

mit uns aufnehmen.

Wer dagegen die Leerplatine oder den Bausatz vor sich

hat, sollte schon über gute SMD-Lötkenntnisse verfügen! Wir

möchten bereits an dieser Stelle darauf hinweisen, daß nur auf

vielfachen Wunsch überhaupt ein Bausatz mit SMD-Bauteilen herausgegeben

wurde und wir keinerlei Haftung oder gar kostenlosen Service für fehlerhaft

oder unprofessionell aufgebaute Platinen übernehmen. Die Schaltung

und die Platine selbst wurden mit größter Sorgfalt hergestellt

und überprüft, daher sind Fehler von dieser Seite grundsätzlich

nicht ausgeschlossen, aber unwahrscheinlich.

Durch die SMD-Bestückung ist die PuPla/2 sehr

klein ausgefallen. Sie arbeitet problemlos mit und ohne PAK, so daß

auch eine Netzwerklösung mit Panther/2 und 68000er alleine möglich

ist.

|

|

|

1.2 |

Lieferumfang |

|

|

Die PuPla/2 gibt es in drei Versionen:

-

Leerplatine, optional mit programmierten GALs

-

Bausatz mit allen Bauteilen

-

Fertiggerät

Optional:

-

PAK-GAL V4-50ac (z.Zt. aktuell)

Die JEDEC-Dateien für die PuPla/2-GALs

sind auch hier erhältlich:

Zur Downloadseite

|

|

|

1.3 |

Voraussetzungen |

|

|

Die PuPla/2 ist für alle Atari-ST Modelle geeignet,

die über einen 68000er-Bus verfügen (also ST, MegaST, STE und

MegaSTE). Für die E-Modelle ist unter Umständen noch eine

PLCC-DIL-Adapterplatine notwendig; wenden Sie sich im Zweifel bitte an uns.

Die PuPla/2 wurde zwar primär für die PAK68/3 entwickelt, es ist

aber auch der Betrieb mit 68000er möglich, um z.B. eine Netzwerkkarte

im Panther/2 interruptfähig zu betreiben.

Die PuPla/2 ist leider ausschließlich

"unter" der CPU - egal ob PAK oder 68000er - betreibbar, da einige

Leitungen unterbrochen werden müssen. Das bedeutet, daß die CPU

in jedem Fall gesockelt sein muß, um die PuPla/2 verwenden zu

können.

Für TT und Falcon ist die PuPla/2 nicht

geeignet!

|

|

|

1.4 |

Funktionsumfang der PuPla/2 |

|

|

-

vollständige Pufferung des Adress- und Datenbus

-

zusätzliche Pufferung der wichtigsten Steuersignale

-

CPU-seitige Dämpfungswiderstände in den Datenleitungen

-

Adresslatch im PAK-Betrieb

-

Konfiguration komfortabel über Jumper

-

Mainboard-Interruptlogik für den Panther/2

-

kleine Abmessungen durch SMD-Bestückung

|

|

2. Aufbau der PuPla/2 |

|

|

2.1 |

Voraussetzungen |

|

|

|

Dieses Kapitel ist für die Besitzer des

Fertiggerätes uninteressant, lesen Sie bitte direkt ab

Kapitel 3 weiter.

Wir gehen davon aus, daß die Leerplatine nur

von Leuten gekauft wird, die wissen was sie da tun und die sich die Bauteile

auch besorgen können. Wer den Bausatz gekauft hat, benötigt

lediglich Erfahrung im Löten von SMD-Bauteilen und die entsprechende

Ausrüstung. Wir möchten nochmals ausdrücklich darauf

hinweisen, daß die Platine und die Schaltung mit größter

Sorgfalt entwickelt und geprüft wurden. Sollte also die

selbstaufgebaute PuPla/2 nicht korrekt funktionieren, ist zu allererst nach

Aufbaufehlern zu suchen. Sollten Sie in so einem Fall unseren Service in

Anspruch nehmen müssen und es stellt sich heraus, daß der Fehler

durch unsachgemäße Bestückung verursacht wurde, ist unsere

Dienstleistung nicht kostenfrei!

|

|

|

2.2 |

Der Aufbau |

|

|

Als Aufbaureihenfolge empfehlen wir zuerst die

SMD-Bauteile auf der Lötseite zu bestücken, anschließend

die SMD-Bauteile auf der Bauteilseite, dann die IC-Adapterstifte auf der

Lötseite und zum Schluß die Sockel/SIL-Streifen auf der

Bauteilseite. Abschließend noch das gewinkelte Pfostenfeld und den

Widerstand unter das PUF-GAL (2k2 von Pin6 zu Pin24 des

PUFCTRL-GALs). Als Tip für die IC-Adapterstifte und die SIL-Streifen:

ein 64-Pin Sockel hilft als Positionierhilfe beim Löten. Weiterhin

ist auf die korrekte Position zu achten: die Stiftleisten zum Mainboard

sind näher zum Platinenrand gelegen.

Die Lage der Bauteile auf der Bauteilseite geht aus

dem Bestückungsaufdruck hervor, die Lage der Bauteile auf der

Lötseite ist leider nur aus dem Bestückungsplan im

Anhang ersichtlich, da aus Kostengründen ein weiterer

Bestückungsaufdruck nicht möglich war. Die Zuordnung der Bauteile

geht aus der Teileliste hervor.

|

|

3. Einbau der PuPla/2 |

|

|

3.1 |

Vorbereitungen |

|

|

Um die PuPla/2 einbauen zu können, muß

die CPU gesockelt sein, weil diese immer auf der PuPla/2 betrieben werden

muß. Sollte das noch nicht der Fall sein, bietet es sich also an,

die CPU-Pins auf beiden Seiten des Prozessors mit einem guten

Seitenschneider vorsichtig direkt am Gehäuse abzukneifen. Die im

Board verbliebenen Pins mit einer Pinzette fassen und auslöten, dann

mit einer guten Pumpe die Löcher freisaugen. Jetzt kann der CPU-Sockel

(Präzisionsfassung!) eingelötet werden. Die original CPU ist jetzt

zwar kaputt, aber ein 8MHz-68000er kostet nicht einmal 10 DM. Und für

diesen geringen Betrag zu riskieren, bei einem Auslötversuch das Board

zu ruinieren, ist eigentlich unnötig. Diese Maßnahme ist die

einzige "Hürde" für den reinen Anwender. Eventuell

läßt sich ja ein löterfahrener Bekannter dazu überreden,

notfalls nehmen Sie bitte Kontakt zu

uns auf. Wir bieten auch einen Einbauservice.

Bevor Sie irgendwelche Arbeiten am Rechner

durchführen, ziehen Sie bitte auf jeden Fall den Netzstecker! Sie

sollten jetzt den Rechner "entkleidet" vor sich haben, um die

PuPla/2 einzubauen.

Die Einbauvarianten sind nach Vorhandensein einer

PAK und der CPU-Bauform des Mainboards geordnet.

|

|

|

3.2 |

Der Einbau ohne PAK / DIL-CPU |

|

|

Der Betrieb der PuPla/2 ohne PAK ist eigentlich

nur sinnvoll, wenn man den Panther/2-ISA-Adapter mit Netzwerkkarte

betreiben will. Dazu muß die PuPla/2 folgendermaßen

konfiguriert werden:

- J1 gesteckt, wenn der Panther/2 oberhalb der PuPla/2 sitzt, im

anderen Fall offen

- J2 offen

- J3 offen

- J4 (unterer Pin) an Pin C3 des Panther/2-Busadapters

Die PuPla/2 kann nun mit der CPU und dem

Panther/2-Busadapter bestückt werden (wir empfehlen den Betrieb

des Panther/2-Busadapters auf der PuPla/2) und anschließend ins

Mainboard gesteckt werden. Damit ist der Einbau abgeschlossen. Es ergibt

sich also als Reihenfolge von 'unten' nach 'oben': Mainboard - PuPla/2 -

Panther/2 - CPU.

Die genaue Bedeutung der Jumper ist in

Kapitel 4.1 erläutert.

|

|

|

3.3 |

Der Einbau mit PAK / DIL-CPU |

|

|

Das dürfte die häufigste Variante sein,

da die PuPla/2 ja als Pufferung für die PAK entwickelt wurde.

Nehmen Sie die PAK aus dem Mainboardsockel und entfernen Sie eine

eventuell vorhandene PuPla/1, sowie eventuell vorhandene Verbindungen

zum Panther/?-Adapter. Konfigurieren Sie die PuPla/2 nun

folgendermaßen:

-

J1 gesteckt, wenn ein Panther/?-Adapter oberhalb der PuPla/2 sitzt,

im anderen Fall offen

-

J2 ist abhängig davon, ob Sie eine 68000 umschaltbar auf der

PAK betreiben, siehe Kapitel 4.1

-

J3 (unterer Pin) an PAK U1 Pin20 über einen 68 Ohm Widerstand

dicht an U1

-

J4 (unterer Pin) an Pin C3 des Panther/2-Busadapters oder offen,

wenn kein Panther/2-Adapter verwendet wird

Nun muß noch das GAL P4 der PAK ausgetauscht

werden, damit das Adresslatch der PuPla/2 funktioniert. Wenn das GAL

V4-50ac im Lieferumfang enthalten war, tauschen Sie es nun gegen das auf

der PAK befindliche GAL U4 aus. Wenn das GAL nicht im Lieferumfang

enthalten war, müssen Sie nun das GAL der PAK selbst auf den neusten

Stand bringen. Die JEDEC-Dateien der PuPla/2, sowie von PAK, FRAK/2 und

des Panther/2-Busadapters sind öffentlich, aber nur zu privater

Nutzung freigegeben. Sie können die

JEDEC-Dateien von unserer

Homepage oder aus dem Mausnetz downloaden (Dateiname:

"WRSGAL??.LZH", ÖPT Maus DO2, 0231- 9252186, Analog & ISDN)

oder mit einem frankierten Rückumschlag und einer einwandfrei

formatierten Diskette per Post bei uns erhalten.

Sie können nun den PAK-Turm wieder

zusammensetzen und in das Mainboard stecken. Damit ist der Einbau

abgeschlossen. Das eventuell vorhanden gewesene Steuersignal vom

Panther/?-Busadapter zur PuPla/1 ist nicht mehr nötig. Die PuPla/2

kann durch J1 alle nötigen Vorkehrungen selbst treffen, damit die

Datenbustreiber von Panther/? und PuPla/2 nicht gegeneinander arbeiten,

wenn der Panther/? oberhalb der PuPla/2 betrieben wird.

Die genaue Bedeutung der Jumper ist in

Kapitel 4.1 erläutert.

|

|

|

3.4 |

Der Einbau ohne PAK / PLCC-CPU |

|

|

In diesem Fall benötigen Sie einen

PLCC-DIL-Adapter. Diese gibt es in zwei großen Gruppen:

Lötfreie Steckadapter und nicht lötfreie (auf

Präzisionssockelpins basierende) Adapter. Ich kann nur dringlich von

ersteren abraten! Diese Adapter bereiten über kurz oder lang

Kontaktprobleme, da eine mechanische Instabilität vorliegt. Leider

ist ein nicht lötfreier Adapter praktisch nirgends zu bekommen.

Notfalls wenden Sie sich an uns. Besitzt man jedoch so einen Adapter,

braucht man für den Einbau sehr gute Löterfahrung und

erstklassiges Werkzeug. Laien auf diesem Gebiet kann ich nur dringlichst

abraten, diesen Umbau zu versuchen! Damit haben sich schon mehrere Leute

ihren geliebten STE getötet...

Sie sehen, bei der PLCC-Bauform der CPU ist der

Einbau leider nicht sehr einfach. Bitte nehmen Sie daher gegebenenfalls

Kontakt zu uns auf.

Haben Sie den PLCC-DIL-Adapter erfolgreich

"implantieren" können, erfolgt der Einbau wie unter 3.2

beschrieben, da ja nun im Prinzip DIL-Bauform vorliegt.

|

|

|

3.5 |

Der Einbau mit PAK / PLCC-CPU |

|

|

Haben Sie bisher eine PuSTE im Einsatz gehabt?

Wenn nicht, dann müssen Sie schon einen PLCC-DIL-Adapter haben, da

ja sonst die PAK nicht benutzbar wäre. In diesem Fall gilt für

Sie das Gleiche wie unter Kapitel 3.3 beschrieben. Wenn Sie aber eine

PuSTE benutzen, müssen Sie diese nun entfernen und gegen einen

PLCC-DIL-Adapter tauschen, da die PuSTE ja im Prinzip eine PuPla/1 ist.

Das ist leider nicht ganz so einfach, wie Sie in Kapitel 3.4 nachlesen

können. Wenn Sie diese Hürde erfolgreich genommen haben, gilt

nun auch das gleiche wie unter Kapitel 3.3 beschrieben.

|

|

4. Konfiguration |

|

|

4.1 |

Jumper |

|

|

Die PuPla/2 wird weitgehend über die

Jumperstiftleiste konfiguriert. Darüberhinaus läßt sich

durch Ändern der GAL-Gleichungen die Konfiguration beeinflussen.

Hier nun zuerst die Erläuterung der Jumperstiftleiste.

Die zweireihige Winkelstiftleiste besteht aus

GND-Pins (obere Reihe) und den eigentlichen Konfigurationspins (untere

Reihe). Die untere Pinreihe ist im Bestückungsaufdruck bezeichnet

mit 1-4. Es gibt zwei unterschiedliche Arten von Pins: Jumper und

Signaleingänge. Bei einem Jumper wird dieser gesteckt oder offen

gelassen, ein Signaleingang erwartet auf dem unteren Pin ein Signal.

Hier die Belegung:

- J1 (Jumper)

- gesteckt: Panther/?-Adapter oberhalb der PuPla/2

- offen, wenn der Panther/?-Adapter unterhalb der PuPla/2 betrieben

wird oder kein Panther/?-Adapter vorhanden ist

- J2 (Jumper oder Signaleingang)

- gesteckt: PAK only, ohne 68000er auf der PAK/FRAK

- offen: 68000er only oder anderer Speeder, aber keine PAK

- Verbindung zur PAK J5 Pin2, wenn eine 68000 umschaltbar auf der

PAK betrieben wird

- J3 (Signaleingang)

- Verbindung zur PAK U1 Pin20 über einen 68 Ohm Widerstand dicht

an U1

- offen, wenn keine PAK betrieben wird

- J4 (Signaleingang)

- Verbindung zu Pin C3 des Panther/2-Busadapters

- offen, wenn kein Panther/2-Adapter verwendet wird

|

|

|

4.2 |

PuPla/2-GALs |

|

|

Die PuPla/2 hat zwei 20v8-GALs für die

Ablaufsteuerung. GAL1, im Bestückungsaufdruck auch mit

"PUFCTRL" bezeichnet, ist für die Steuerung der

Pufferungsfunktionen zuständig. Die aktuelle Gleichung für

dieses GAL heißt "PUF2-004". GAL2, im

Bestückungsaufdruck auch mit "AVICTRL" bezeichnet,

ist für die Steuerung der Interruptfunktionen zuständig.

Leider hat sich die aktuelle Gleichung seit der Auslieferung bereits

verändert und heißt "AVI5-06b". In den ersten

Tests hat sich gezeigt, daß dieses GAL in einer ganz

bestimmten Situation einen Busfehler (zwei Bomben) zulassen kann:

wenn unter starker Last in die Netzwerkkarte geschrieben wird. Bei

normaler bis mittlerer Last und beim Lesen aus der Karte tritt dieser

Effekt nicht auf. Der Grund für dieses Verhalten ist recht

merkwürdig. Die "a"-Version der AVI5-Gleichung

bestätigt einen Autovektorinterrupt Level 5 nur, wenn das

Interruptsignal der Karte noch anliegt. Das hat den Vorteil, daß

auch ein Nonautovektor auf der selben Ebene möglich ist. Es scheint

nun aber so, als würde die Karte die Interruptanforderung vor der

Bestätigung zurücknehmen können (eben nur unter starker

Last), so daß die CPU den Interruptacknowledge-Zyklus nicht

bestätigt bekommt (das gibt dann die Bomben). In der

"b"-Version der Gleichung wird nun immer eine

Interruptbestätigung der Ebene 5 als Autovektor gefahren. So

kommt man ohne das Interruptanforderungssignal der Netzwerkkarte aus.

Das verhindert die Busfehler, aber leider kann nun kein

Nonautovektorinterrupt Ebene 5 mehr ausgelöst werden. Diese

L”sung ist nicht weiter schlimm, denn uns ist keine Erweiterung

bekannt, die diese Anforderungen stellt.

Sollten Sie nicht in der Lage sein, das AVI-GAL

der PuPla/2 auf den aktuellen Stand zu bringen, können Sie ein

kostenloses GAL-Update bei uns bekommen.

|

|

Anhang A - Bestückungsplan |

|

|

Die Bestückungspläne sind als GEM-Image Datei

verfügbar: Zur Downloadseite.

|

|

Anhang B - Stückliste |

|

|

| Position |

Anzahl |

Bezeichnung |

| GAL1, GAL2 |

2 |

GAL20V8-15ns |

| IC1, IC2 |

2 |

74HCT373-SMD |

| IC3 |

1 |

74HCT573-SMD |

| IC4, IC5 |

2 |

74F245-SMD |

| R1 - R16 |

16 |

Widerstand 100 Ohm SMD 1206 |

| R17 - R20 |

4 |

Widerstand 4,7 kOhm SMD 1206 |

| |

1 |

Widerstand 2,2 kOhm |

| C1 - C6 |

6 |

SMD-Kondensator 100 nF, 1206 |

| für die GALs |

2 |

DIL-Sockel 24pin schmal |

| PAK |

2 |

SIL-Sockel 32pin |

| Mainboard |

2 |

Steckadapter SIL 32pin |

| CON1 |

1 |

Pfostenleiste zweireihig, 8pin, gewinkelt |

| |

2 |

Jumper dazu |

|

|

Zuletzt geändert am 08.03.2007, RS

|